Active SMD Packages (Microchip)

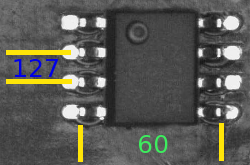

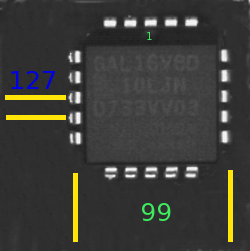

udg8_127p60x16

udg8_127p60x16- "Microchip" Dual Gull-wing with 8 pins, 1.27mm Pitch, 6.0mm Pin over Pin, 1.6mm High

- Old Zen: so8_60x16

- Small Outline with 8 pins...

- The package known as SO8. The once very common pitch of 1.27mm separates old style Zentroid package names. Smaller pitch packages are named "sop" for "Small Outline Packages" and lop for "Large Outline Packages".

- Since ""so" is the division point always having a pitch of 1.27mm the Zentroid SMD Naming Convention drops the pitch entry in the "so" names. The new Zentroid names are not divided and the pitch is always included in the name.

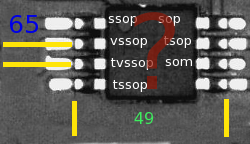

udg8_65p49x15

udg8_65p49x15- "Microchip" Dual Gull-wing with 8 pins, 0.65mm Pitch, 4.9mm Pin over Pin, 1.5mm High

- Old Zen: sop8_65p49x15

- Small Outline Package with 8 pins...

- The name indicates almost exactly which package is in question. Have you ever tried to define rules for the characteristics of SO, SOM, SOP, SOL, SOLIC, SSOP, VSOP, TSOP or TSSOP? Manufactures, Ipc and others will likely never agree on the limits and tolerances so why bother?

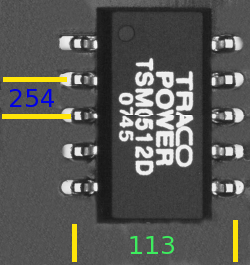

udg10_254p113x70

udg10_254p113x70- "Microchip" Dual Gull-wing with 8 pins, 2.54mm Pitch, 11.3mm Pin over Pin, 7.0mm High

- Old Zen: lop10_254p113x70

- Large Outline Package with 10 pins...

- Ever wondered what prompted someone to call a package SOL? I mean semantic horror. It is a small outline but large!

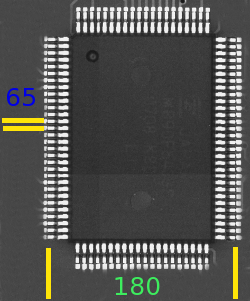

uqg100_65p180x34

uqg100_65p180x34- "Microchip" Quad Gull-wing with 100 pins, 0.65mm Pitch, 18.0mm Pin over Pin, 3.4mm High

- Old Zen: qfp100_65p180x34

- Quad Flat Pack with 100 pins...

- A lot of qfp packages are square but not all. The Zentroid SMD Naming Convention uses the number of pins, pitch, pin over pin width and the height to name a qfp/uqg package. This is enough information in almost all package definitions of this form.

- Polarity is again left and upper if possible.

- One other point of note is the faint print on the package. Print on a package may not be indicative of pin number one of the package. Print orientation is a last resort to checking package orientation.

uqj20_127p99x46

uqj20_127p99x46- "Microchip" Quad J-leg with 20 pins, 1.27mm Pitch, 9.9mm Pin over Pin, 4.6mm High

- Old Zen: plc20_127p99x46

- Plastic Leaded Chip Carrier with 20 pins...

- "plc" just seems to be the natural short form for the traditional name. Note the small number 1 in the picture. This pin can be the number 1 pin or pin 1 can be in the left and upper corner of the package. For this reason the bevelled side of this package is positioned to the top when the package is in its zero degree orientation.

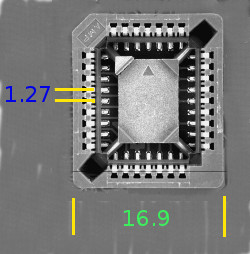

uqj32_127p169x45soc

uqj32_127p169x45soc- "Microchip" Quad J-leg with 20 pins, 1.27mm Pitch, Overall width 16.9mm, 4.5mm High, Socket

- Old Zen: plc20_127p99x46

- Plastic Leaded Chip Carrier with 20 pins...

- I have found that keeping the component name and adding the suffix "soc" works the best. If you have found the component add the suffix and you can easily search or find the matching socket nearby.

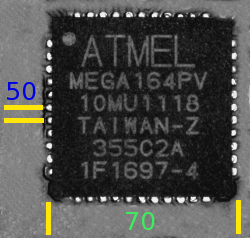

uql44_50p70x12

uql44_50p70x12- "Microchip" Quad Leadless with 44 pins, 0.50mm Pitch, 7.0mm Pin over Pin, 1.2mm High

- Old Zen: lcc44_50p70x12

- Leadless Chip Carrier with 44 pins...

- You might know this package as "Qfn" or "Lcc". Atmel has another package out that is called a "DRQFN". It is a slightly smaller package that has 2 rows of "staggered pitch" pins on all 4 sides of the package. The Zentroid SMD Naming Convention uses the name ugl44_35sp50x09 for such packages.